はじめに

今週の半導体チップ雑談は、インターポーザのお話。その中で、TSMCのCoWoSの件。現在は、CoWoS-S で、これからは CoWoS-L が出てくると

TSMCの2023のAnnual Reportを見て確認してみたいと思います。

CoWoS-S と CoWoS-L

51頁の5.2 Technology LeadershipのCoWoS のところに、下記のようにありました

CoWoS® advanced packaging service is the leading 2.5D technology to make ultra-high-performance AI and HPC packages by integrating most advanced logic and memory dies on an interposer. Market demands became even greater with the advent of generative AI in late 2022. TSMC qualified the CoWoS®-S Si interposer up to 3.3-reticle size (1 reticle size ~830mm2), with volume production launched in 2023. Beyond 3.3-reticle size, CoWoS®-L with reconstituted interposer of multiple LSIs (local silicon interconnects) increases the momentum for continuous interposer scaling. After its successful development in 2023, the first generation CoWoS®-L technology will enter volume production in 2024. HBM3E, the newest generation of high bandwidth memory, is ready now for production on both CoWoS®-S and CoWoS®-L, while the next generation of stacked memory of HBM4 and process upgrades in CoWoS® advanced packaging service are being planned to meet new performance requirements.

CoWoS-S 3.3-recticle size は、2023年に量産。3.3-recticle size を超えるものは、CoWoS-L ? .CoWoS-Lは2023に開発に成功し、2024年に量産に入ると、

2022年のAnnual Report の8頁には、

For our advanced packaging technologies, the

CoWoS®-S technology that integrates multiple system-on-chip (SoC) chips, high bandwidth memory stacks, and a 3-reticle size silicon interposer successfully entered volume production for customer HPC products in 2022.

また、51頁には、

The new third generation HBM3 was certified on CoWoS-S in 2022. In parallel, CoWoS-L with multiple local Si interconnects (LSIs) embedded in an organic interposer are being developed. Compared with CoWoS-S, CoWoS-L dramatically improved the size limitation of a Si interposer and enabled more features in an interposer to boost overall system performance.

とある。

2022年では、HBM3 + 3-recticle、2023年では、HBM3e + 3.3-rectile ということだったのね。

2021年のAnnual Report では、

The CoWoS® Gen-5 with a Si interposer area up to 2,500mm2 to accommodate at least two SoC logic and eight HBM stacks was qualified in 2021. The new HBM3 (third generation HBM) certification on CoWoS® will be a major focus for TSMC in 2022.

2021年では、2,500mm2 (3-rectile)+ HBM3 を開発

ということで、2021 (3-rectile + HBM3開発)=> 2022 (3-rectile+HBM3量産) => 2023 (3.3-rectile+HBM3e量産)

AMD の MI200は

2021年11月11日の下記のブログでも取り上げましたが、AMDのMI200シリーズ。2 die + HBM x8 です。2021年なのでTSMCの3-rectileは開発途中。ということはAMDはTSMCの技術を使っていないということですかね。

vengineer.hatenablog.com

CoWoS-S x4 は無くなったの?

community.cadence.com

の中に下記のスライドがあります。説明のために引用します。

2020年のスライドで、3x rectile (8 HBM)は2021年、4x rectile (12 HBM) は 2023年とあります。3x rectile は 2021年開発、2022年量産とありますが、その次が 4x ではなく、3.3x で 2023年量産です。

そして、3.3x を超えるのは、CoWoS-S ではなく、CoWoS-L になると。。。

おわりに

ずーと、x12 HBM は、CoWoS-S x4 だと思っていましたが、3x => 3.3x というステップになっていることから、4x の量産は難しいと判断し、CoWoS-L にシフトしたということでしょうかね。。。

2022年からCoWoS-Lの開発をしていたようなので、何となく、そんな感じでは?と思います。。。

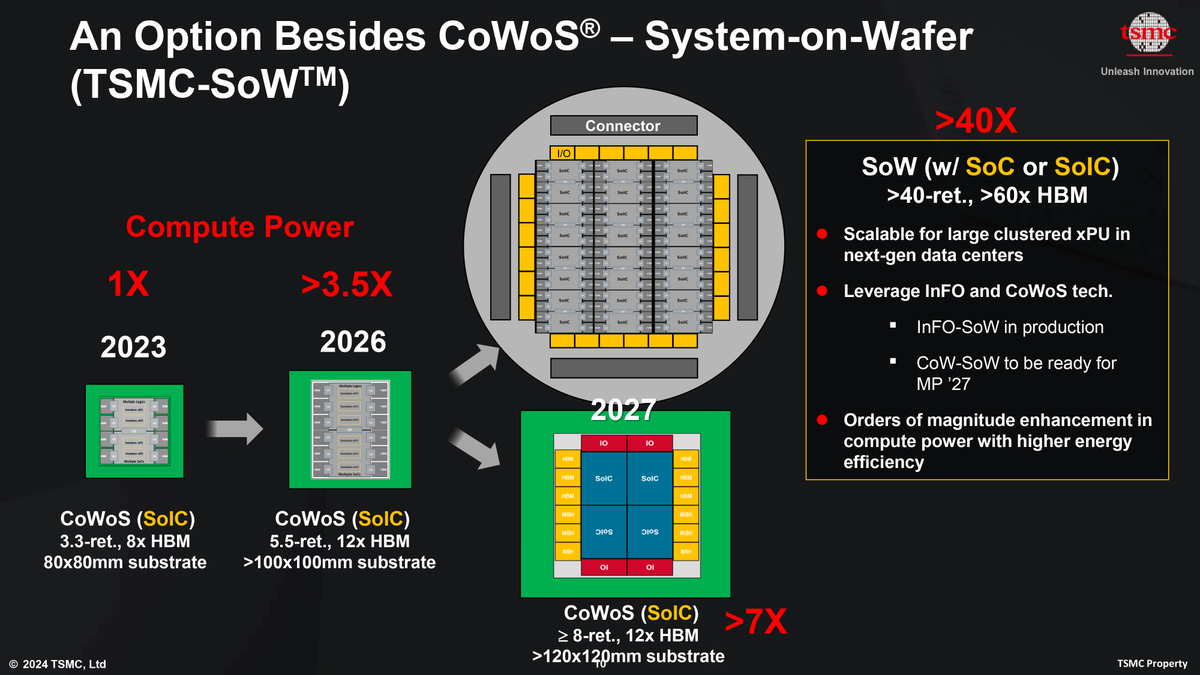

下図は、TSMC to go 3D with wafer-sized processors — CoW-SoW technology allows 3D stacking for the world's largest chipsから説明のために引用します。Tesla Dojo Chip の SoW (System-on-Wafer) の説明スライドで、CoWoSと比較するためのものだと思います。

- CoWoS : 3.3-ret., 8x HBM (2023)

- CoWoS : 5.5-ret., 12x HBM (2026)

- CoWoS : >= 8-rect., 12x HBM (2027)

とありますね。ここでは、CoWoS-S とは書いてありませんね。ということは、